CDM 测试(2)

这是一个从case开启的故事。前段时间跟一个同行聊CDM测试,一颗产品CDM只能pass 200V。参考以往测试经验,虽说一些射频相关或带高速接口的芯片,接口的ESD能力会稍差,但小封装一般CDM的等级500V基本能保证,对照如此差异,不得不再度打开了JEP157的等级检查。

IC对高速IO的不断增长的需求,以及单个封装中集成更多功能的需要,推动封装尺寸变大,CDM测试能力也受到相应的挑战。

图片引自《JEP157》

高速接口的ESD能力为何较差?

RF 高速设计比标准高速 SERDES 设计更具限制性,而相比于其他电路,他们的ESD能力会较低,这要与使用的ESD保护电路联系起来。

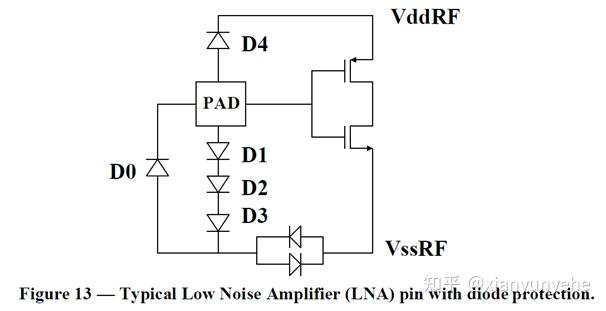

二极管的寄生电容主要来自于PN结的结电容,与带有栅结构的GGNMOS相比,可以算寄生电容很小的一类器件。这个特点对射频电路的ESD防护尤其重要,因为任何外加寄生电容电感的引入都会对射频电路的性能产生影响。低噪声放大器 (LNA) 输入电路尤其不耐受 ESD 保护器件电容。 在这些电路中,ESD 地通常与 LNA 地隔离,并由二极管隔开,如下图:

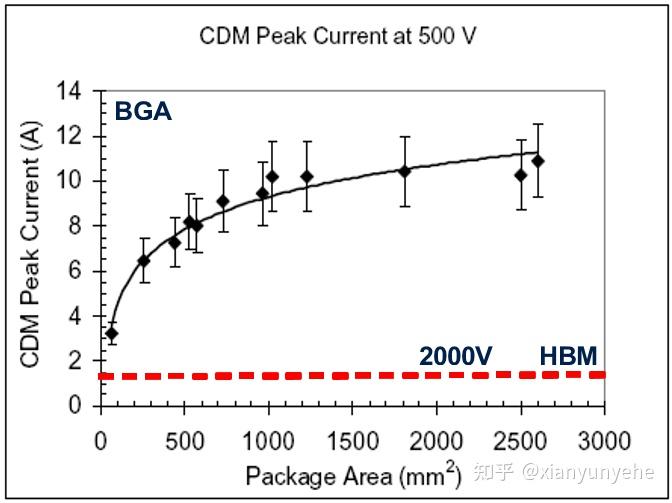

SoC的 RF 芯片通常用8mm * 8mm 或 10mm * 10mm 的较小 BGA 封装。峰值电流非常低,在 500V 时不超过 3~4 A。峰值电流限制,会影响到CDM的能力,下图为在500V下,BGA封装尺寸大小和峰值电流的对应关系。

CDM等级要求的原因?

现在回到最开始的问题,CDM能力的要求在JEP157中明显降低的原因。

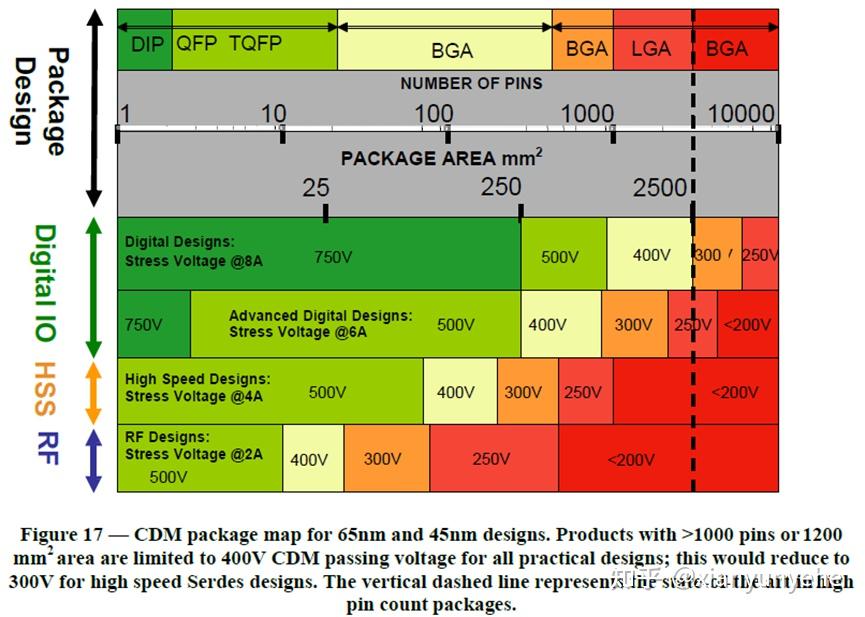

1. IC 元件的引脚数和封装尺寸显着增长。在给定的预充电压下 ,峰值电流是限制芯片CDM(尤其是封装尺寸)的敏感函数。pin数量和封装尺寸增大,会使IC存储更多的电荷,CDM泄放时峰值电流迅速增加。因而在峰值电流同等的情况下,pin数量、尺寸越大,CDM能力越低。

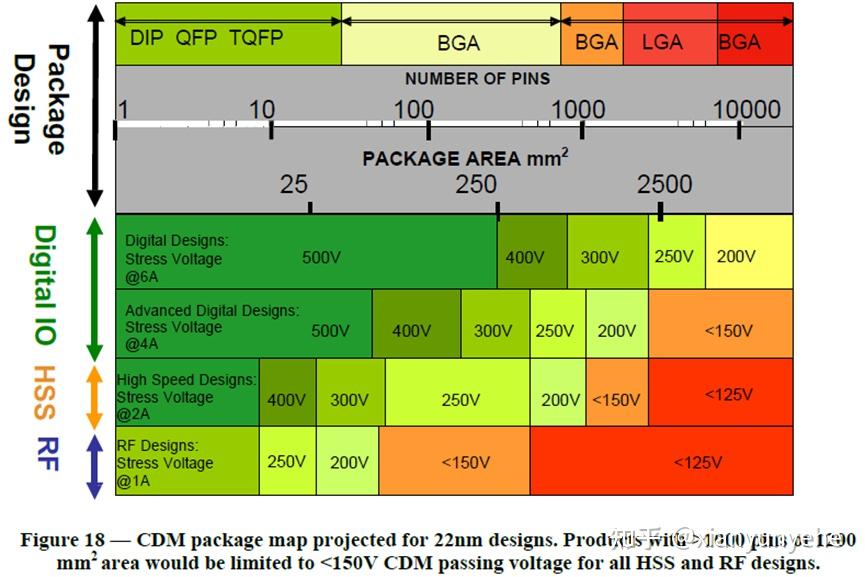

2. IC 工艺技术的进步。从JEP157的roadmap可以看出,随着工艺尺寸的缩小,CDM能力显著降低。工艺尺寸减小,导致有源器件更小、更脆弱,另外更薄、更具电阻性的金属互连,降低了 ESD电路的稳健性。使得在给定电流水平下,CDM 保护变得更加困难。

3. 具有高速数字、RF 模拟和其他性能敏感引脚的混合信号 IC 日趋普遍。对于高频电路,将 ESD 保护器件直接连接到 I/O 引脚会导致 RF 功能严重下降, 因此,需要将射频保护结构与核心电路隔离。通常通过在 ESD 器件和引脚间插入并联电感/电容网络实现。 这种网络在低频 ESD 作用中提供接近零的阻抗,在正常高频操作中提供接近无穷大的阻抗。

封装类型、芯片种类、封装尺寸、pin数量等之间的相关关系对照如下,两张图分别为65nm&45nm和22nm以下的情况:

JEP157内容还是挺厚实的,大家可以多研究研究,附录中还有一些系统ESD&CDM、CDM&EOS的失效case对比。

******************************************************************************************

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

欢迎小窗咨询探讨可靠性方案~

参考文献:

新ANSI/ESDA/JEDEC JS-002 CDM测试标准概览 | 亚德诺半导体 (analog.com)

带电器件模型(CDM)的测试与防护 - 道客巴巴 (doc88.com)

《集成电路ESD防护设计理论、方法与实践》

JS-002-2018-CDM Charged Device Model (CDM) - Device Level